- #1

reddvoid

- 119

- 1

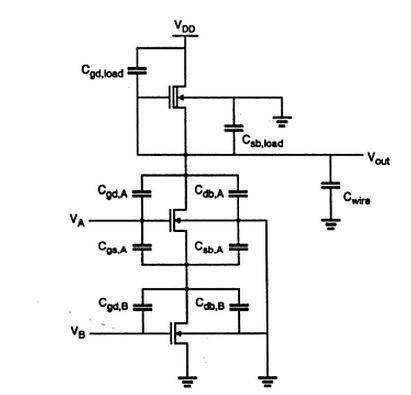

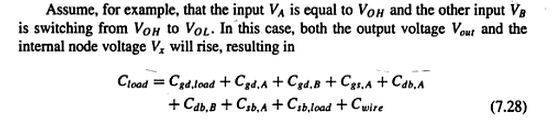

Why we are not writing Cgs Cdb in depletion mode nmos here

why no Csb in bottom nmos

Can somebody please explain how to write which components of Cload or provide some links from where i can understand it better

thank you,

this picture is from http://books.google.co.in/books?id=XUruXhP2s6gC&lpg=PP1&pg=PA285#v=onepage&q&f=false

why no Csb in bottom nmos

Can somebody please explain how to write which components of Cload or provide some links from where i can understand it better

thank you,

this picture is from http://books.google.co.in/books?id=XUruXhP2s6gC&lpg=PP1&pg=PA285#v=onepage&q&f=false