- #1

perplexabot

Gold Member

- 329

- 5

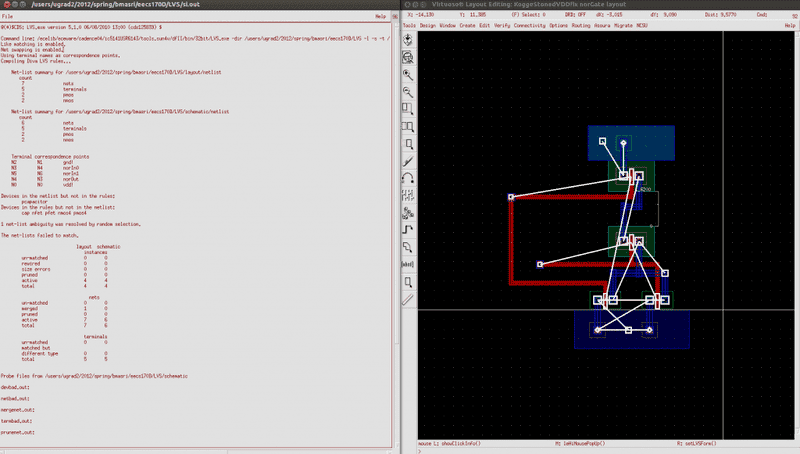

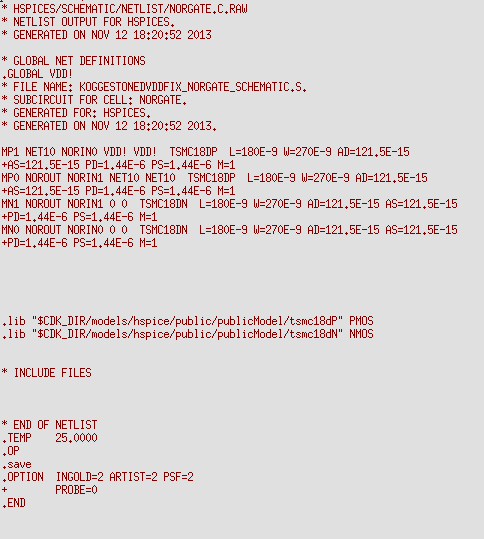

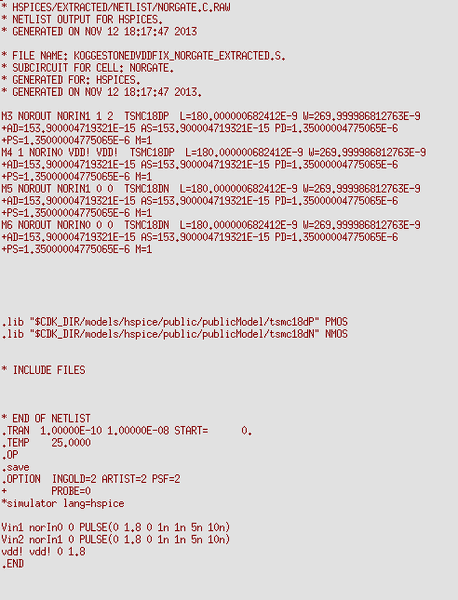

Hello all. I have been at this layout all day and I have seriously had it. So half way through the day I realized and confirmed that it is the source to body connection of the middle pmos that is missing (i think), the problem is I don't know how to make that connection! Simple, but I have tried every google search combination possible, there is absolutely nothing about this online! I will attach my layout and the netlists for comparison. Please any help will be much appreciated.

PS: I know my layout is poorly constructed.

EDIT: Forgot to mention, DRC is successful.

PS: I know my layout is poorly constructed.

EDIT: Forgot to mention, DRC is successful.