- #1

- 2,116

- 2,691

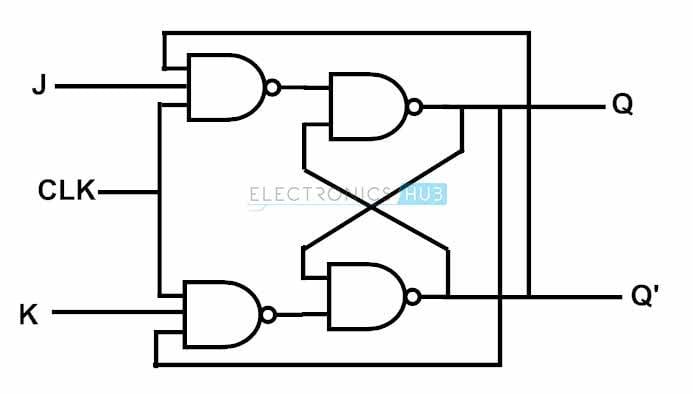

Our exercise in lab today was to construct a JK flip-flop using basic NAND gates. The ICs we used were 74LS00 and 74LS10. The circuit diagram we used is this:

We were, however, not getting the expected values of Q and Q' based on the values of J, K and CLK. For instance, in my case, CLK=1, J=1 and K=0 gave Q=1, as expected. But the moment I put CLK to GND, both Q and Q' went up to the HIGH state, irrespective of the values of J and K. We checked our circuit as well as the ICs, but there was no fault in either one.

Some other groups were facing the same issue as us, although for some specific set of input values only. Other groups were facing a different issue: suppose after setting J=1 and K=0, when they set J=1 and K=1 (the toggle state), both outputs went up to 1. In short, the toggle state was always giving Q=Q'=1.

The errors were occurring randomly, in the sense that not all groups had the exact same wrong output for a particular set of input values. If a group changed ICs, they often got the wrong output(s) for a different set of input values.

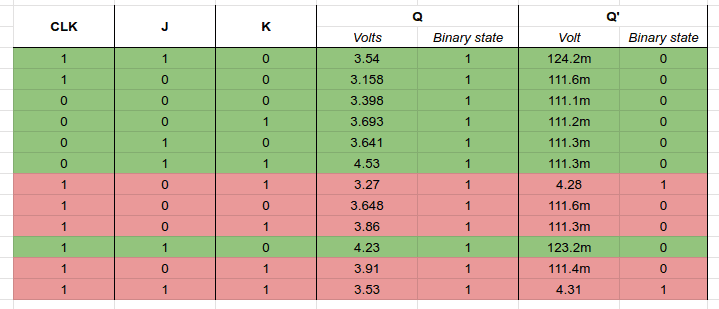

I brought two ICs home to see if I can re-create the issue. I used a 5V supply from an Arduino Mega. This is what I got:

The green rows indicate that the measured state is the same as the expected state. Red indicates that the measured state and expected state does not agree. The inputs are written exactly in the sequence they were applied. Hence, some input values are repeated. A number followed by "m" implies mV, otherwise V.

As you may see, this is not the same as what I got in class today. But I was getting the values consistently. E.g., if I set CLK=1, J=1 and K=1, I consistently got Q=Q'=1 irrespective of what the previous state was.

Some of my classmates were saying that a master-slave JK flip-flop will solve this. The Prof. hasn't given any answer yet.

Why is this happening? Race condition between the transistors used in the ICs? What can we do to prevent this?

We were, however, not getting the expected values of Q and Q' based on the values of J, K and CLK. For instance, in my case, CLK=1, J=1 and K=0 gave Q=1, as expected. But the moment I put CLK to GND, both Q and Q' went up to the HIGH state, irrespective of the values of J and K. We checked our circuit as well as the ICs, but there was no fault in either one.

Some other groups were facing the same issue as us, although for some specific set of input values only. Other groups were facing a different issue: suppose after setting J=1 and K=0, when they set J=1 and K=1 (the toggle state), both outputs went up to 1. In short, the toggle state was always giving Q=Q'=1.

The errors were occurring randomly, in the sense that not all groups had the exact same wrong output for a particular set of input values. If a group changed ICs, they often got the wrong output(s) for a different set of input values.

I brought two ICs home to see if I can re-create the issue. I used a 5V supply from an Arduino Mega. This is what I got:

The green rows indicate that the measured state is the same as the expected state. Red indicates that the measured state and expected state does not agree. The inputs are written exactly in the sequence they were applied. Hence, some input values are repeated. A number followed by "m" implies mV, otherwise V.

As you may see, this is not the same as what I got in class today. But I was getting the values consistently. E.g., if I set CLK=1, J=1 and K=1, I consistently got Q=Q'=1 irrespective of what the previous state was.

Some of my classmates were saying that a master-slave JK flip-flop will solve this. The Prof. hasn't given any answer yet.

Why is this happening? Race condition between the transistors used in the ICs? What can we do to prevent this?