- #1

CraigHB

- 94

- 19

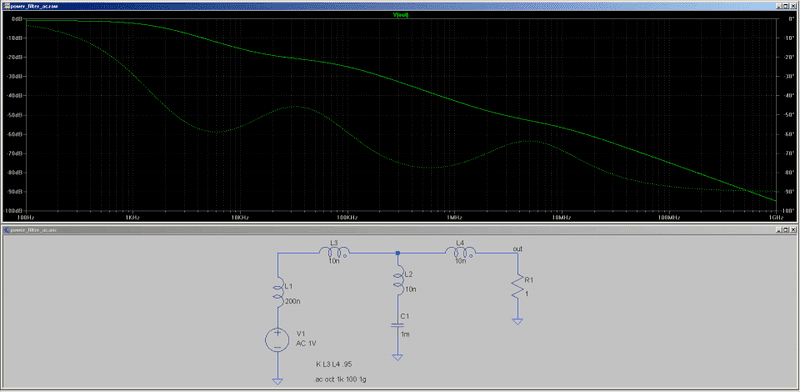

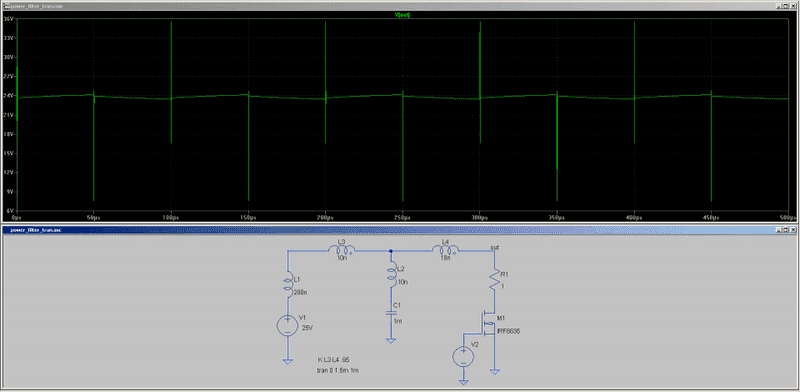

I'm trying to set up a DC power supply filter for a 2kW motor controller. I'm trying to set up inductance cancelling for the input capacitor array. When I simulate the coupled T filter in the frequency domain I get what I expect to see. However when I simulate the transient response I'm still getting voltage spikes due to input capacitor ESL. I'm not understanding why the filter is failing to attenuate those. Can someone please explain to me what's happening? See attached plots below.

TIA,

- Craig

TIA,

- Craig